## RF SoC FPGA 기반의 고속 신호 수신기 구현

최소연\*, 김기영\*\*, 권은상\*\*, 유호영\* 충남대학교 전자공학과\*, 대명티에스\*\*

# Implementation of High-Speed Signal Receiver using RF SoC FPGA

Soyeon Choi\*, Kiyoung Kim\*\*, Eunsang Kwon\*\*, and Hoyoung Yoo\* Dept. of Electronics Engineering, Chungnam National University\*, Daemyeong TS\*\*

E-mail: soyeonchoi@cnu.ac.kr, giyoung.kim@dmtsc.com, etri76312@etri.re.kr, hyyoo@cnu.ac.kr

#### Abstract

In this paper, we implement a high-speed signal receiver using RF SoC FPGA and show the result. Recently, as the number of systems using high-frequency signals increases, the need for high-speed signal receivers also increases. When the RF stage and the base-band stage are separately developed, problems such as signal distortion occurs during signal transmission. Therefore, a high-speed signal receiver is implemented using the ZCU208 evaluation board including RF ADC/DAC that can develop the RF and baseband parts on one chip. The digitized data is transferred to the DDR memory of the core using DMA and stored data in the DDR memory transmitted to the PC through UART interface. The sampling frequency of the ADC is set to 1.96608 GHz, and the core frequency is set to 1.2 GHz. As a result of the experiment, it was confirmed that the input signal was received without distortion.

#### I. 서론

신호 수신기의 설계는 아날로그 신호를 수신이 필요한 모든 어플리케이션에 필수적인 요소이다. 최근, 고주파대역의 신호를 사용하는 시스템이 증가함에 따라고속의 신호 수신기의 개발 또한 필수적이다 [1]. 대부분의 고속 신호 수신기는 별도의 ADC (Analog-to-converter)를 이용하여 고주파 대역의 아날로그 신호를 수신하여 디지털 신호로 변환하고, 그 신호

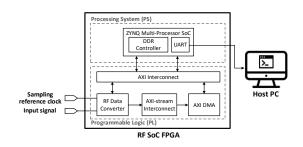

그림 1. RF SoC 기반의 고속 신호 수신기

를 디지털 신호 처리를 위한 기저대역부(base-band stage)로 전송한다. 기저대역부는 수신한 데이터를 처리하여응용 시스템을 구동하는 PC 로 전송한다. 그러나 신호의 주파수 대역이 높아질수록 RF 인터페이스에서 신호가 왜곡되는 등의 문제가 발생하였다 [2]. 본 논문에서는 이러한 문제점을 보완하기 위하여 하나의 칩으로 RF 대역의 신호를 수신하여 처리할 수 있는 RF SoC FPGA를 사용한 고속 신호 수신기를 구현하였다.

#### II. RF SoC 기반의 고속 신호 수신기

Xilinx 사에서 개발한 RF SoC FPGA 는 RF 대역의 신호 수신을 위한 RF 부와 기저대역부를 그림 1 과 같 이 하나의 칩으로 개발할 수 있다. RF SoC FPGA 내부는 구성가능한 회로를 구현하는 PL(programmable logic) 부 분과 core 를 포함하는 PS(processing system)으로 구성된 다. PL 부분은 RF 대역의 신호를 송/수신하는 14-bit

이 논문은 2021 년도 정부(교육부)의 재원으로 한국연 구재단의 지원을 받아 수행된 기초연구사업임 (No. 2021R1I1A3055806).

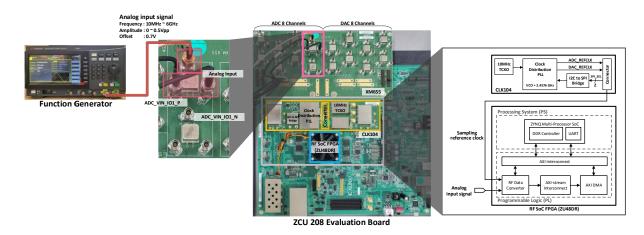

그림 2. ZCU208 평가보드를 활용한 고속 신호 수신기

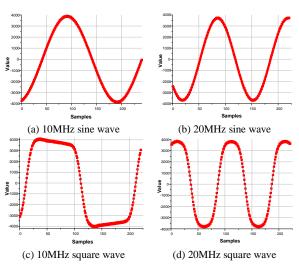

그림 3. 신호 수신 결과

ADC/DAC (Analog-to-Digital Converter, Digital-to-Analog Converter), 입/출력 구현 회로, 구성가능한 논리회로 등으로 구성된다. PS 부분은 ARM 코어와 UART, SATA, USB 와 같은 인터페이스, 메모리 컨트롤러로 구성된다.

고주파 대역의 신호를 수신하기 위해서는 PL 부분의 ADC/DAC 를 이용하여 회로를 구현해야 한다. 그림 1 은 본 논문에서 구현한 RF SoC 를 이용한 고속 신호수신기의 블록다이어그램을 나타낸다. RF 신호 수신을위한 RF ADC/DAC 는 RF Data Converter(RFDC)로 구현가능하며, 샘플링 주파수, 사용할 ADC/DAC 채널 수 등을 설정하여 구현할 수 있다. RFDF로 처리된 데이터는 AXI stream interconnect를 이용해 AXI DMA (Direct Memory Access)블록으로 전달된다. 해당 신호는 DMA를 통해 core 에 연결된 DDR 메모리로 전달된다. DDR 메모리에 쓰여진 데이터는 UART 인터페이스를 통해응용시스템이 구현된 PC로 전달된다.

### III. 실험 결과 및 결론

본 논문에서는 Xilinx 사의 ZYNQ RF SoC FPGA 인 ZU48DR FPGA가 구현된 ZCU 208 평가보드를 사용하여그림 2 와 같이 고속 신호 수신기를 실제로 구현하였다. 해당 FPGA는 10MHz 대역의 신호부터 최대 6 GHz 대역의 신호까지 수신 가능하다. RF ADC의 동작을 위한샘플링 주파수는 CLK104 보드를 평가보드에 장착하여생성하고, 아날로그 신호는 XM655 보드를 평가보드에장착하여 수신하였다. RF ADC의 샘플링 주파수는 1.96608GHz로 설정하였으며, 코어와 DDR 메모리의 동작주파수는 각각 1.2GHz, 533MHz로 설정하였다.

그림 3 은 고속 신호 수신기를 구현한 평가보드에 실제 정현파와 사각파를 인가하였을 때 UART 를 통해 수신한 결과를 재 구현한 파형이다. 10MH 와 20MHz 의신호는 각각 한 주기에 약 196 개의 샘플, 약 98 개의샘플로 수신한 아날로그 신호를 디지털로 변환하였다. 본 논문에서는 RF SoC에 내장된 RF ADC의 동작을 검증하였으며, 이를 통해 하나의 칩으로 아날로그 입력신호를 수신하고 처리하는 것이 가능함을 검증하였다.

#### 참고문헌

- [1] B. Farley, J. McGrath and C. Erdmann, "An All-Programmable 16-nm RFSoC for Digital-RF Communications," in *IEEE Micro*, vol. 38, no. 2, pp. 61-71, Mar./Apr. 2018.

- [2] S. Pulipati et al., "Xilinx RF-SoC-based Digital Multi-Beam Array Processors for 28/60 GHz Wireless Testbeds," 2020 Moratuwa Engineering Research Conference (MERCon), 2020, pp. 254-259.